- 您现在的位置:买卖IC网 > Sheet目录3886 > PIC16LCE624-04E/SO (Microchip Technology)IC MCU CMOS 1K OTP W/EEPRM18SOIC

1999 Microchip Technology Inc.

DS40182C-page 73

PIC16CE62X

NOP

No Operation

Syntax:

[

label ]

NOP

Operands:

None

Operation:

No operation

Status Affected:

None

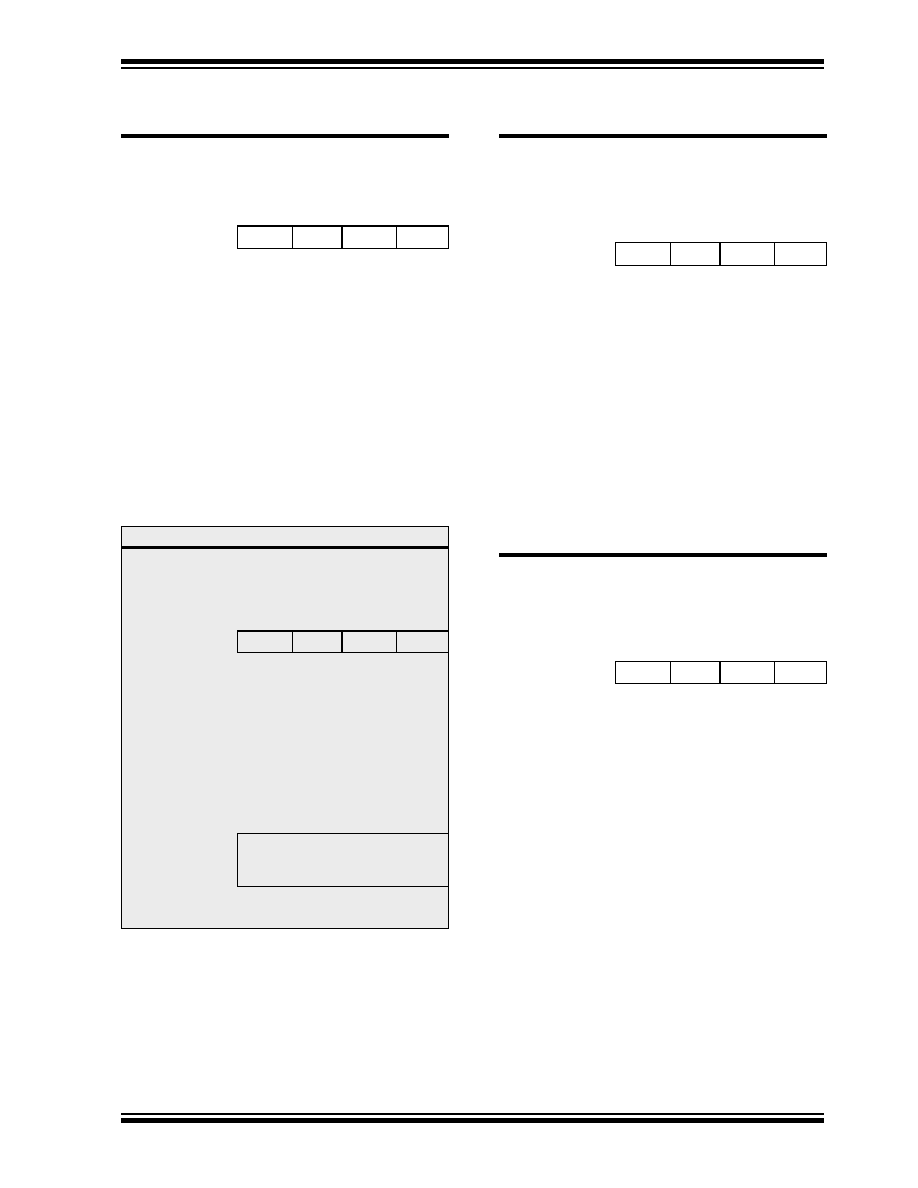

Encoding:

00

0000

0xx0

0000

Description:

No operation.

Words:

1

Cycles:

1

Example

NOP

OPTION

Load Option Register

Syntax:

[

label ]

OPTION

Operands:

None

Operation:

(W)

→ OPTION

Status Affected: None

Encoding:

00

0000

0110

0010

Description:

The contents of the W register are

loaded in the OPTION register. This

instruction is supported for code

compatibility with PIC16C5X products.

Since OPTION is a readable/writable

register, the user can directly

address it.

Words:

1

Cycles:

1

Example

To maintain upward compatibility

with future PICmicro products, do

not use this instruction.

RETFIE

Return from Interrupt

Syntax:

[

label ]

RETFIE

Operands:

None

Operation:

TOS

→ PC,

1

→ GIE

Status Affected:

None

Encoding:

00

0000

1001

Description:

Return from Interrupt. Stack is POPed

and Top of Stack (TOS) is loaded in

the PC. Interrupts are enabled by

setting Global Interrupt Enable bit,

GIE (INTCON<7>). This is a two-cycle

instruction.

Words:

1

Cycles:

2

Example

RETFIE

After Interrupt

PC =

TOS

GIE =

1

RETLW

Return with Literal in W

Syntax:

[

label ]

RETLW k

Operands:

0

≤ k ≤ 255

Operation:

k

→ (W);

TOS

→ PC

Status Affected:

None

Encoding:

11

01xx

kkkk

Description:

The W register is loaded with the eight

bit literal ’k’. The program counter is

loaded from the top of the stack (the

return address). This is a two-cycle

instruction.

Words:

1

Cycles:

2

Example

TABLE

CALL TABLE

;W contains table

;offset value

;W now has table

value

ADDWF PC

;W = offset

RETLW k1

;Begin table

RETLW k2

;

RETLW kn

; End of table

Before Instruction

W

=

0x07

After Instruction

W

=

value of k8

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F1829-I/SO

MCU PIC 14K FLASH 1K RAM 20SOIC

PIC16F685-I/SS

IC PIC MCU FLASH 4KX14 20SSOP

PIC16LCE624-04E/P

IC MCU CMOS 1K OTP W/EEPRM 18DIP

PIC16F689-I/SS

IC PIC MCU FLASH 4KX14 20SSOP

PIC16C54C-04I/SO

IC MCU OTP 512X12 18SOIC

PIC16C54C-04/SO

IC MCU OTP 512X12 18SOIC

PIC16F722-I/ML

IC PIC MCU FLASH 2KX14 28-QFN

PIC16LCE623T-04I/SO

IC MCU CMOS.5K OTP W/EEPRM18SOIC

相关代理商/技术参数

PIC16LCE624-04E/SS

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624-04I/P

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624-04I/SS

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624T-04/SO

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624T-04/SS

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624T-04E/SO

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LCE624T-04E/SS

功能描述:8位微控制器 -MCU 1.75KB 96 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT